# A NOVEL STRATEGY FOR MULTILEVEL CASCADED INVERTERS (MLCI) UNDER UNBALANCED DC SOURCES

### A.Manoj<sup>1</sup>, K V Sai Kumar<sup>2</sup> PG Student, KITE, Kakinada, India. Asst.Professor, Department of EEE, KITE, Kakinada, India.

*Abstract:* This paper introduces a pulse width-modulation strategy to achieve balanced line-to-line output voltages and to maximize modulation index over the range of linear modulation where the output voltage can be linearly adjusted in the multilevel cascaded inverter (MLCI) functioning under unbalanced dc-link conditions. In these conditions, the linear modulation range is lowered, and a considerable output voltage imbalance may occur as voltage references increase. In order to study these effects, the voltage vector space for MLCI is examined in detail. From this analysis, the theory behind the output voltage imbalance is analyzed, and the maximum linear modulation range obtainable taking into consideration an unbalanced dc-link condition is evaluated. Thereafter, a strategy based on neutral voltage modulation is introduced to obtain the output voltage balance and as to extend the linear modulation range up to the maximum point in theory. In this method, very large dc-link imbalance distorts the balancing of the output voltages. This limitation is also discussed. The simulation for a seven-level phase-shifted modulated MLCI for electric vehicle traction drive illustrate that the proposed method proves to be efficient in balancing the line-to-line output voltages and also in maximizing the range of linear modulation involving the unbalanced dclink conditions. *Keywords: Linear* Modulation Range, MLCI, PWM.

#### **I.INTRODUCTION**

Multilevel inverters enable the synthesis of a sinusoidal output voltage from several steps of voltages. Owing to this factor, the multilevel inverters have low dv/dt ratings and usually have low harmonics in the output voltage and current. Also, the switching of very high voltages is made possible by stacking of multilevel inverter modules. Due to these advantages, multilevel inverters have been applied in various application fields. Among various multilevel inverters schematics, the multilevel cascaded inverter (MLCI) topology is one of the prominent topologies due to its simple design for modularization and tolerance to faults. The modulation strategy in MLCI applications, to generate gate signals is very crucial to achieve high-performance control.

In most cases, PWM strategy based on carrier or SVPWM is suited for applications such as motor drives, where dynamic properties are very important, while SHEPWM strategy is suitable for some high-power static power conversion applications. To reduce the common-mode voltage, a multilevel SVPWM has been proposed. The series SVPWM method has been reported to easily implement SVPWM for the MLCI. Normally, SVPWM is implemented for hybrid inverters consisting of neutral point clamp and Hbridge inverters in order to improve output voltage efficiency and quality. As with two-level inverters, it is also possible to operate carrier-based SVPWMs which are proportional to traditional SVPWMs by injecting a common offset voltage to the three-phase references MLCIs require distinct dc links. Hence, if there are one or more faults present in the dc links in respective phase or in cases asymmetry is observed in the voltage magnitudes of the dc links, the output voltage reference, which considers a zero sequence voltage to mitigate the imbalance in magnitude of output voltage and an offset voltage to extend the linear modulation range, can be calculated. In the present method, very large dc-link imbalance precludes the

output voltages from being balanced. Therefore, if this scheme is applied to applications such as EV traction systems, the dynamic characteristics can be greatly improved.

### **II.SYSTEM DESCRIPTION**

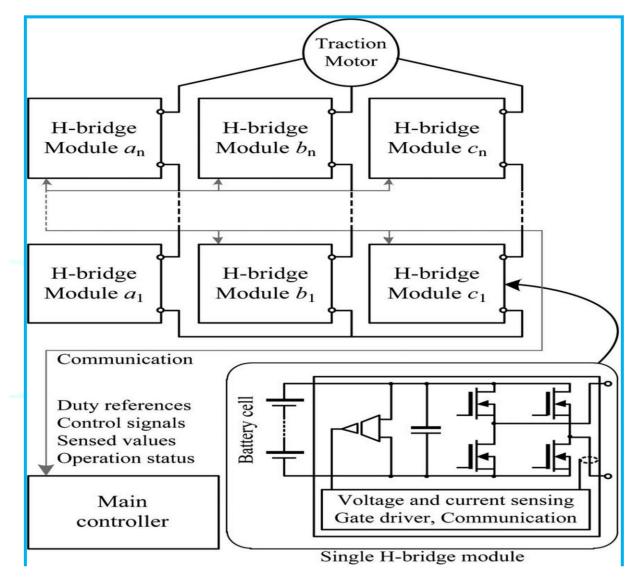

The MLCI- based inverter for EV Traction Drive is shown in fig 1 below.

In this configuration, various power ratings can be easily implemented by configuring the number of the single H-bridge modules according to a required specification such as an EV traction drive, sedan, and so on. Here, each H-bridge module has voltage and current sensors, gate drives, and communication interfaces between the module itself and the main controller. It also consists of battery cells. The unipolar modulation technique is applied in the H-bridge module between two switching legs. As a result of this, the effective switching frequency in each H-bridge module is two times that of the carrier frequency. In addition to this, the well-known PS modulation technique is used to implement multilevel operation.

Therefore, the effective switching frequency *f*sw in a phase is

$$Fsw = 2N \times fc$$

(1)

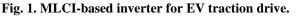

Where *N* and *fc* represent the number of the H-bridge modules in each phase and the carrier frequency of PWM, respectively. Fig. 2 below illustrates the carriers for each module, the duty cycles in unipolar modulation, and the output voltage when N = 2.

### III.PROPOSED NOVEL STRATEGY FOR MLCI CASCADED INVERTERS UNDER UNBALANCED DC SOURCES

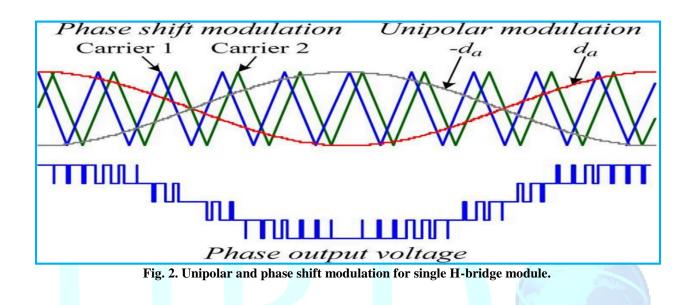

A novel strategy is proposed to realize the maximum value of modulation index in the range of linear modulation under the unbalanced conditions. The offset voltage injection scheme is a famous technique in three-phase half-bridge inverter applications. The principle behind this is that an offset voltage is incorporated with phase voltage references to implement various PWM schemes in carrier-based PWM by making use of the fact that line-to-line voltages are applied to a three-phase load [1], [2]. Consider, the offset voltage  $v^* sn$  is used to the phase voltage references  $v^*as$ ,  $v^*bs$ , and  $v^*cs$  to implement carrierbased SVPWM as in

$$v_{sn}^{\star} = \frac{v_{\max}^{\star} + v_{\min}^{\star}}{2} \qquad v_{\max}^{\star} = \max\left(v_{as}^{\star}, v_{bs}^{\star}, v_{cs}^{\star}\right) \tag{2}$$

$$v_{\min}^{\star} = \min\left(v_{as}^{\star}, v_{bs}^{\star}, v_{cs}^{\star}\right).$$

Fig. 3. Implementation of the NVM Method.

Now, the voltage references at pole i.e. $v^*$  an,  $v^*bn$ , and  $v^*cn$ , which will be converted to PWM duty references, are

$$v_{an}^{*} = v_{as}^{*} - v_{sn}^{*} \quad v_{bn}^{*} = v_{bs}^{*} - v_{sn}^{*} \quad v_{cn}^{*} = v_{cs}^{*} - v_{sn}^{*}.$$

<sup>(3)</sup>

In case the unbalanced dc links in an MLCI and the conventional offset voltage injection methods are utilized, the three-phase output voltages would be distorted due to the factor that the phase voltage reference approaches *V*ph\_max. This is because the traditional methods do not take into account dc-link conditions when unbalanced. Therefore, even if a phase can synthesize the reference voltage at output in the range of linear modulation, the remaining phases can besaturated or go into the over modulation region. In this condition, a neutral voltage can be developed by the saturated or overmodulated phase. In order to resolve this issue and to synthesize the output voltage to *V*ph\_max in the range of linear modulation, the NVM technique is proposed in this paper. Fig. 3 shows the concept of the proposed NVM technique.

The neutral voltage between the two neutral points n and s is modulated to compensate the output voltage imbalance caused by unbalanced dc-link conditions. Making use of this fact, the proposed method lowers the portion of the phase whose dc-link voltage is lower than the others and maximizes the utilization of the phase in which the dc-link voltage is greater than those of the other phases. However, v'sn does not affect the line-to-line voltages. Therefore, the line-to-line voltage is the same as the one obtained from the original phase voltage reference. From this analysis, the proposed method enables the maximum synthesizable modulation index in the linear modulation range under the unbalanced dc-link conditions to be achieved. Also, if all the voltages of dc-link are well balanced so that  $Vdc_a$ ,  $Vdc_b$ , and  $Vdc_cc$  are equal to Vdc.

#### **IV.SIMULATED PERFORMANCE**

(4)

### Journal Of Electrical And Electronics Engineering

A simple one-by-three configuration MLCI model is built in Matlab Simulink. The three-phase *RL* load with  $R = 0.1\Omega$  and L = 1mH is employed. The dc-link voltages for each phase are  $Vdc_a = 0.5 \times 30$  V,  $Vdc_b = 0.75 \times 30$  V, and  $Vdc_c = 30$  V. The maximum synthesizable phase voltage in linear is

$$V_{\rm ph\_max} = \frac{0.75 \times 30 + 0.5 \times 30}{\sqrt{3}} = 21.65 \,\mathrm{V}.$$

The voltage references are given by

$$v_{as}^{*} = V_{\rm ph\_max} \sin(100\pi t)$$

$$v_{bs}^{*} = V_{\rm ph\_max} \sin(100\pi t - 2\pi/3)$$

$$v_{cs}^{*} = V_{\rm ph\_max} \sin(100\pi t + 2\pi/3).$$

(5)

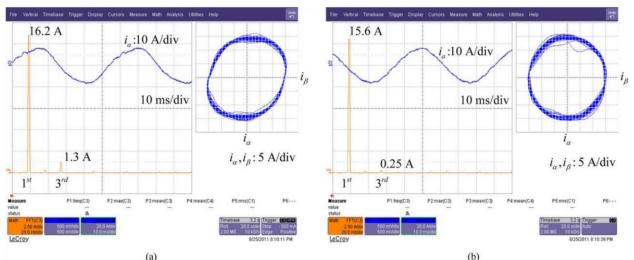

The conventional SVPWM gives more area than SPWM.However, the voltage distortion is unavoidable. This method shows no distortion in the output voltage and maximizes the voltage vector space compared to other methods. The time-domain simulation results are illustrated below. The time range from t = 0.05 secs, the conventional SPWM is used. The time range from t = 0.05 secs tot = 0.1 secs, conventional SVPWM is used. After the time t = 0.1 secs, the proposed method is applied. With conventional SVPWM, the voltage  $v^*sn$  is not zero anymore, and the peak value of the pole voltage references is reduced compared to SPWM. But in both cases, the duty reference of phase a, where the dclink voltage is least among the three phases, is saturated. Whileusing the proposed method however, the duty references are not saturated because the fundamental frequency component of the neutral voltage is included in  $v^*sn$ .

The benefit of the proposed method can be analyzed from the peak value of the phase current in the final part of the figure. Under conventional methods, the phase currents are unbalanced. But, with the proposed method the phase currents are well balanced. From the simulation outputs, it is clear that the proposed method can obtain the maximum obtainable phase voltage in the linear modulation range under unbalanced dc link.

Fig. 4. Comparison of the FFT results and the current trajectories in the  $\alpha - \beta$  plane. (a) Traditional carrierbased SVPWM. (b) Proposed NVM.

#### **V.CONCLUSION**

The NVM technique under unbalanced dc-link conditions for MLCIs has been proposed in this paper. In order to analyze the maximum synthesizable voltage of MLCIs, the analysis of voltage vector space is done using the switching function. This proves that the maximum linear modulation range was derived. The proposed NVM technique is used to obtain the maximum modulation index in the linear modulation range under an unbalanced dc-link condition and also to balance the output phase voltage. Compared to the previous methods, the proposed technique is easy to implement and the output voltage quality profile under unbalanced dc-link conditions is improved. Both simulations and experimental results conducted on the IPM motor drive application verify the effectiveness of the proposed method.

#### REFERENCES

[1] D.-W. Chung, J.-S. Kim, and S.-K. Sul, —Unified voltage modulation technique for real-time threephase power conversion, *IEEE Trans. Ind. Appl.*, vol. 34, no. 2, pp. 374–380, Mar./Apr. 1998. [2] F. Wang, —Sine-triangle versus space-vector modulation for three-level PWM voltage-source inverters, *IEEE Trans. Ind. Appl.*, vol. 38, no. 2, pp. 500–506, Mar./Apr. 2002. [45] F. Carnielutti, H. Pinheiro, and C. Rech, —Generalized carrier-based modulation strategy for cascaded multilevel converters operating under fault conditions, *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 679–689, Feb. 2012.

- [3] J.-S. Lai and F. Z. Peng, —Multilevel converters—A new breed ofpower converters, *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, May/Jun. 1996.

- [4] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, —A surveyon cascaded multilevel inverters, *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [5] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. León, R. C. Portillo, M. A. M. Prats, and M. A. Perez,

- —Multilevel converters: An enabling technology for high-power applications, *Proc. IEEE*, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

- [6] G. Bergna, E. Berne, P. Egrot, P. Lefranc, A. Arzande, J.-C. Vannier, and M. Molinas, —An energybased controller for HVDC modular multilevel converter in decoupled double synchronous reference frame for voltage oscillation reduction, *IEEE Trans. Ind. Electron.*, vol. 60, no. 6, pp. 2360–2371, Jun. 2013.

- [7] Z. Shu, N. Ding, J. Chen, H. Zhu, and X. He, —Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM, *IEEE Trans. Ind. Electron.*, vol. 60, no. 5, pp. 1884–1896, May 2013.

- [8] J. Chavarria, D. Biel, F. Guinjoan, C. Meza, and J. J. Negroni, —Energybalance control of PV cascaded multilevel grid-connected inverters under level-shifted and phase-shifted PWMs, *IEEE Trans. Ind. Electron.*, vol. 60, no. 1, pp. 98–111, Jan. 2013.

- [9] J. Rodriguez, J.-S. Lai, and F. Z. Peng, —Multilevel inverters: A survey of topologies, controls, and applications, *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [10] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, —Medium-voltage multilevel converters— State of the art, challenges, and requirements in industrial applications, *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010. CHO *et al.*: CARRIER-BASED NVM STRATEGY FOR MLCIS UNDER UNBALANCED DC SOURCES 635